# 國立中央大學九十學年度碩士班研究生入學試題卷

所別: 通訊工程研究所 不分組 科目: 電子學 共 工 頁 第 / 頁

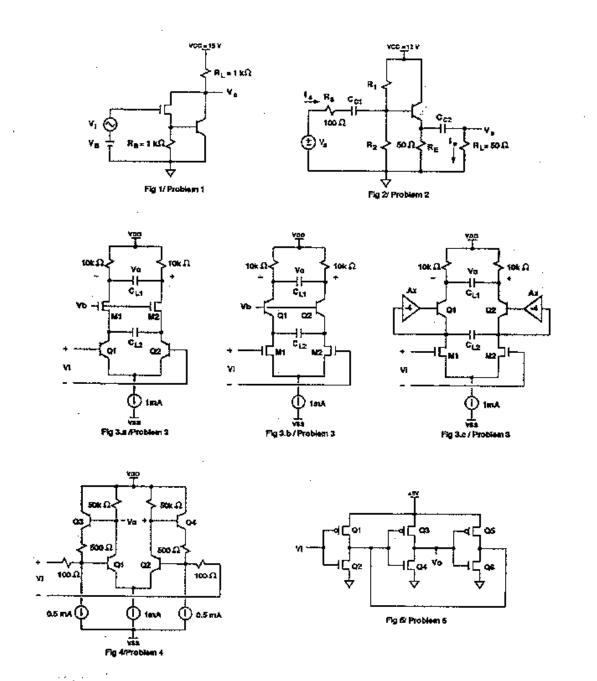

## 1. (15%)

Consider the BiCMOS circuit shown in Fig. 1. The bias voltage  $V_B$  is adjusted for a dc output voltage of 2 V and  $R_B=1$  K $\Omega$ . The transistor parameters are:  $\mu_n C_{ox}=60$   $\mu A/V^2$ , W = 40  $\mu m$ , L = 1  $\mu m$ , and  $V_{TH}=0.8$  V for MOSFET, and  $I_S=10^{-16}$  A,  $\beta_F=100$ .

- (a) Calculate the bias currents in both transistors, ID1 and IC1.

- (b) Calculate the small-signal voltage gain  $v_a/v_b$

- (c) Find out the output resistance R<sub>o</sub>.

- 2. (15%)

If the Early voltage  $V_A = 100 \text{ V}$  and the common-emitter current gain  $100 \le \beta_F \le 180$ ,  $V_{BE(on)} = 0.7 \text{ V}$

- (a) Please design the emitter-follower circuit (Fig. 2) (choose the appropriate values of  $R_1$ ,  $R_2$  and  $\beta_F$ ) such that the minimum current gain  $A_i = i/i_T = 10$ .

- (b) The input signal source is given by  $v_s = V_m \sin w_o t$ , determine the maximum value of  $V_m$  that will produce a symmetrical sinusoidal output signal.

## 3. (25%)

Consider the circuit shown in Fig 3, assume MOSFETs are operating in saturation region and BJTs are operating in forward active region,  $\mu_n C_{ox} W/L = 25 \text{ mA/V}^2$  for all MOSFETs,  $\beta = 100$  for all BJTs,  $V_T = 25 \text{ mV}$ ,  $C\pi = Cgs = 0.5 \text{ C}_{L2}$  << CL1 and  $C\mu = Cgd << C_{L2}$ , neglect ro. Ccs and Cds.

(5%) (a) The small signal DC gain of amplifier 3.a and 3.b are A1 and A2 respectively, which statement is correct? (1) A1 > A2 (2) A1 < A2 (3) A1= A2 (答出何和 2%) (5%) (b) The phase margin of amplifier 3.a and 3.b are  $\phi$ 1 and  $\phi$ 2 respectively,  $\phi$ 2=60°, which statement is correct? (1)  $\phi$ 1 >  $\phi$ 2 (2)  $\phi$ 1 <  $\phi$ 2 (3)  $\phi$ 1 =  $\phi$ 2 (答错例和 2%)

(15%)(c) Assume amplifier 3.b has a 3dB bandwidth of 10kHz and a phase margin of 60°, inverting amplifier Ax has a 3dB bandwidth of 600 MHz and a small signal DC gain of -4, neglect the loading effect of Ax, what is the resulting 3dB bandwidth (5%) and phase margin (10%) of amplifier 3.c.

#### 4. (15%)

Consider the circuit shown in Fig 4, assume  $V_T = 25$  mV and  $\beta = 100$  for Q1-Q4. (a) What kind of feedback topology (shunt-shunt, series-shunt, shunt-series, series-series) is utilized in this amplifier? (5%)

(b) Small signal DC gain Vo/Vi = ? (10%)

## 5. (15%)

In the CMOS bistable circuit shown, all transistors have |Vt| = 1 V and, with k = 1/2 k' (W/L),  $k1=k2=k3=k4=2k5=2k6=200 \mu \text{ A}' \text{ V}^2$ , (a) Sketch and label the volatage transfer characteristic of the Q3-Q4 inverter. (5%)

## 國立中央大學九十學年度碩士班研究生入學試題卷

所別: 通訊工程研究所 不分組 科目: 電子學 共 一 頁 第 一 頁

- (b) Sketch and label the transfer characteristic Vo versus Vi. (5%)

- (c) Find the ViH and Vil. (5%)

## 6 (15%)

A particular two-input NOR gate has  $t_{PHL} = 1$  ns and  $t_{PLH} = 3$  ns. Five such gates, each with one input low, are connected in cascade to form a ring.

- (a) Find the oscillation frequency. (5%)

- (b) Two additional such gates, A and B, are connected to the ring, gate A inputs to the outputs of gates 1 and 3, and gate B inputs to the outputs of gates 1 and 4. Sketch and label the waveforms at all NOR gate outputs. (10%)